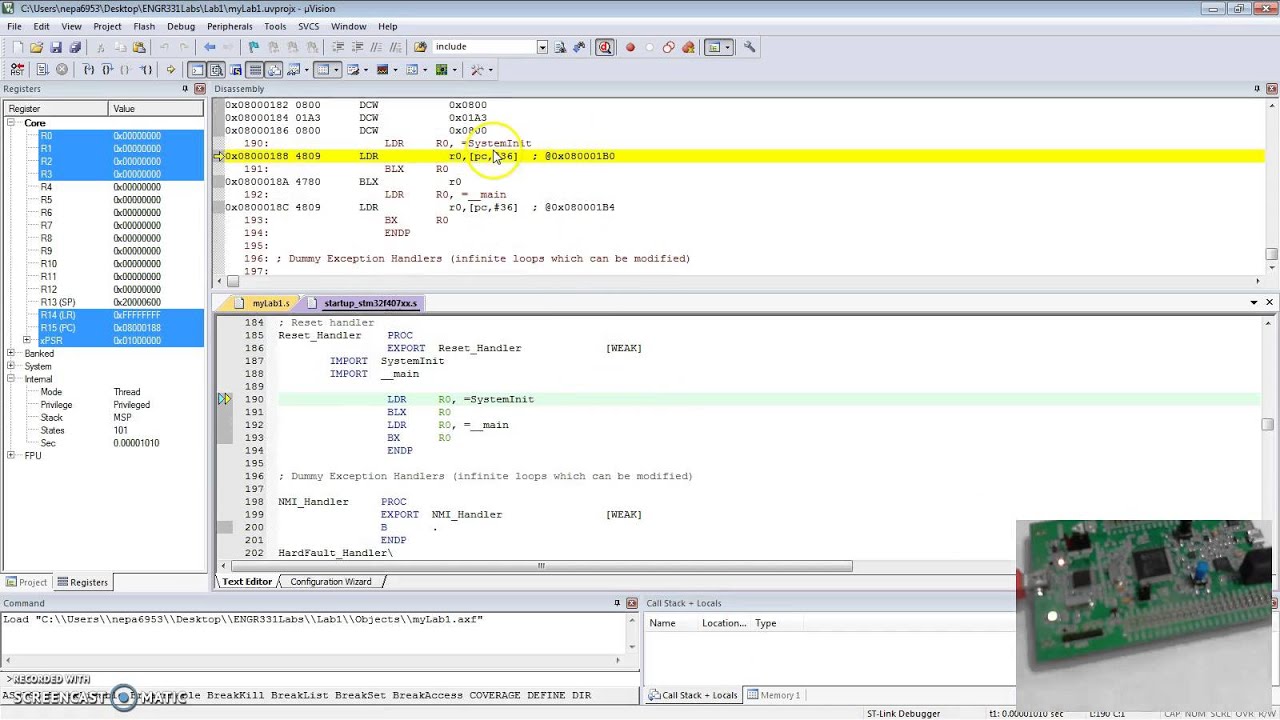

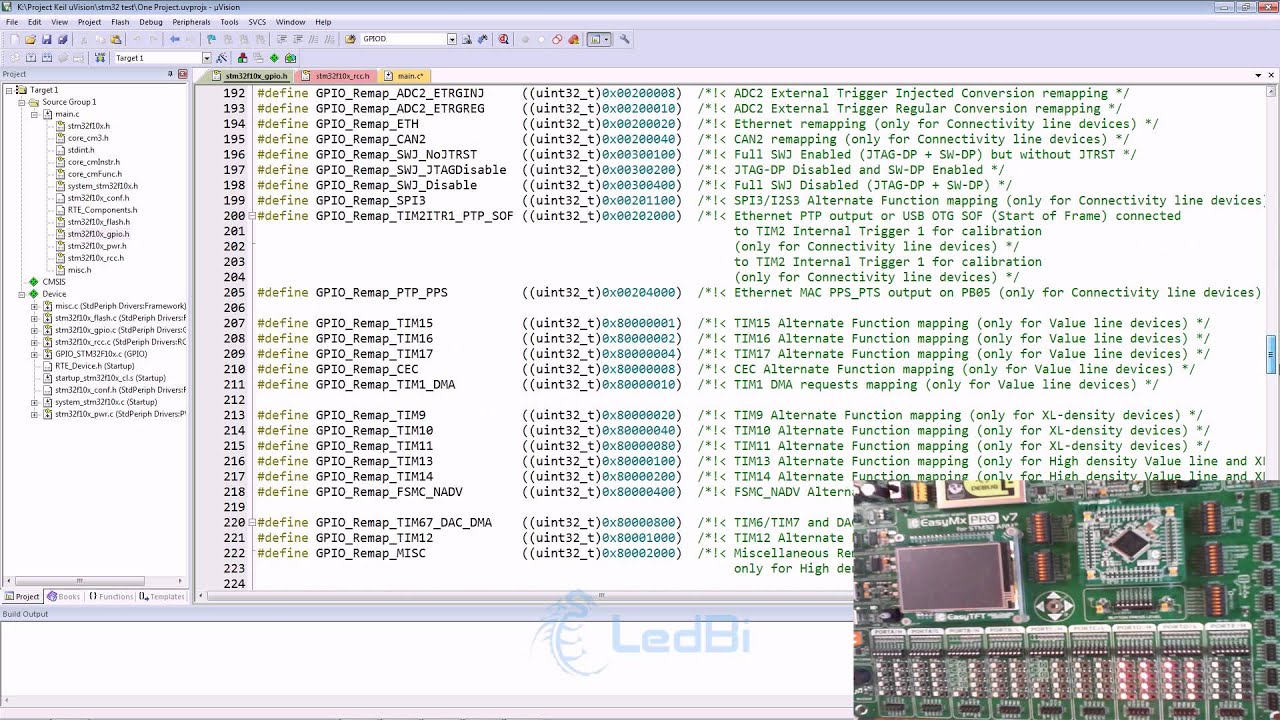

The specific events or conditions to watch for are programmable by the user from the debugger interface. Watching – Bus event detectors are used to watch for certain events occurring in the system. The developer can program complicated scenarios and is limited only by the amount of logic on the device used for this capability. The developer can program the event counters and comparators from the user interface. The host debugger provides the graphical display of the source code, the processor resources, memory locations, peripheral status, etc.įigure 9.9.

Keil 5 debug stops software#

The host software runs the debugger software and interfaces to the on-chip debug registers through the dedicated interface header. On-chip debug also requires a host system to communicate with and control the debug session and extraction of data. These may be the JTAG port pins and perhaps some additional pins dedicated to control or data. Communication between the chip and the debugger host requires additional pins on the DSP device.

Keil 5 debug stops code#

These resources include capability available to the end user code such as breakpoint registers and other dedicated hardware. The functionality that resides on the DSP itself is hardware implemented resources. On-chip debugging is actually a combination of both hardware and software. This is referred to generally as on-chip debug. Given the vanishing visibility in today's sophisticated DSP processors, debug capability is moving onto the chip itself. Robert Oshana, in DSP Software Development Techniques for Embedded and Real-Time Systems, 2006 On-Chip Emulation Capability When the cursor is again on the Delay10KTCYx function, press F8 to skip to the next instruction without displaying the contents of this function. Press F7 to execute the PORTD = 0xFF instruction (the LEDs will turn ON). When the debug cursor (green arrow) is on the Delay10KTCYx function, press F8 to skip to the next instruction without displaying the contents of this function. Select PORTD and click Add SFR to add PORTD to the watch window (see Figure 5.36). Set the values of PORTD to be displayed during the debugging. Press F7 to single-step through the program. Press F7 key several times until the C code is displayed in the debug window. Select Debugger -> Program to load the code into the target microcontroller. Select Project -> Build All to rebuild the project in Debug mode. Select Project -> Build Configuration -> Debug.

The program should be compiled and run in single-step debug mode. The circuit diagram and the program listing are as in Figures 5.34 and 5.35, respectively. The vector catch mechanism is commonly used by the debugger to halt the processor at the beginning of a debug session, immediately after the program is downloaded and the processor is reset.Īfter debugging is completed, program execution can be returned to normal by clearing the C_HALT bit in DHCSR. It is controlled by a register called Debug Exception and Monitor Control Register (DEMCR, at address 0圎000EDFC) see Table 14.5. This is a programmable feature that, when enabled, can halt the processor right after a system reset, or when certain fault exceptions occur. However, this can be connected to accept debug events from additional debug components (chip manufacturers can add extra debug components to the SoC) or, if the design is a multi-processor system, it could be linked to debug events from another processor.Īnother debug event available is called Vector Catch.

In some cases, this signal could be tied low and never occur. The actual connection of this signal depends on the microcontroller or SoC design.

One of the debug events is an external debug request signal, called EDBGREQ on the Cortex-M3/M4 processor.

0 kommentar(er)

0 kommentar(er)